| Latency(CLK) | 0 |

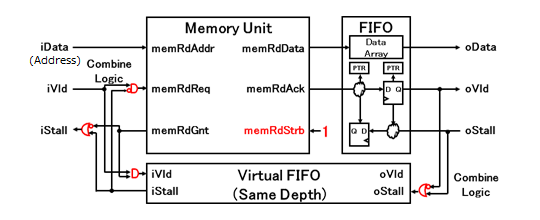

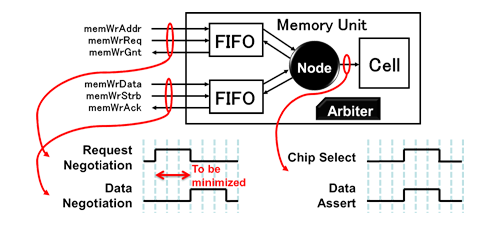

module wrMem(

iAdData, iAdVld, iAdStall,

iDtData, iDtVld, iDtStall,

memAddr, memReq, memGnt,

memData, memStrb, memAck,

reset, clk);

input [31:0] iAdData; // Address

input iAdVld;

output iAdStall;

input [31:0] iDtData; // Write Data

input iDtVld;

output iDtStall;

output [31:0] memAddr;

output memReq;

input memGnt;

output [31:0] memData;

output memStrb;

input memAck;

input reset;

input clk;

wire adVld;

wire dtVld, dtStall;

wire vaVld, vaStall;

wire vdVld, vdStall;

fifo adFifo ( // Address FIFO

.iData (iAdData),

.iVld (iAdVld),

.iStall (iAdStall),

.oData (memAddr),

.oVld (adVld),

.oStall (!memAdGnt | !vaVld | vdStall),

.reset (reset),

.clk (clk)

);

fifo dtFifo ( // Data FIFO

.iData (iDtData),

.iVld (iDtVld & !vaStall),

.iStall (dtStall),

.oData (memData),

.oVld (dtVld),

.oStall (!memDtAck | vdStall),

.reset (reset),

.clk (clk)

);

sig vaFifo ( // Virtual Address FIFO

.iVld (iDtVld & !dtStall),

.iStall (vaStall),

.oVld (vaVld),

.oStall (!memAdGnt | !adVld | vdStall),

.reset (reset),

.clk (clk)

);

sig vdFifo ( // Virtual Data FIFO

.iVld (memGnt & adVld & vaVld),

.iStall (vdStall),

.oVld (vdVld),

.oStall (!memAck | !dtVld),

.reset (reset),

.clk (clk)

);

assign iDtStall = dtStall | vaStall;

assign memReq = adVld & vaVld & !vdStall;

assign memStrb = dtVld & vdVld;

endmodule

|