抶墑偺堏摦偲偼

- 摨婜愝寁偵偍偄偰榑棟怺搙偺曃傝偼丄偄偔偮偐偺儃僩儖僱僢僋傪敪惗偝偣傑偡丅撍弌偟偨1偮偺儃僩儖僱僢僋偩偗偱FF偺Setup帪娫偑戝偒偔側傝丄晄岾偵傕嵟戝摦嶌廃攇悢傪墴偟壓偘傞偙偲偑懡乆偁傝傑偡丅

- 偙偙偱偼丄慡懱偺抶墑僶儔儞僗傪峫偊偨愝寁[1]偑偁傞掱搙偱偒偰偍傝丄榑棟崌惉偵傛傝儃僩儖僱僢僋偑攃埇偱偒偰偄傞傕偺偲偟傑偡丅偙偙偱偼丄榑棟婰弎偺峔憿傪曄偊偢偵丄娙扨偵抶墑挷惍偡傞曽朄[2][3][4]傪帵偟傑偡丅

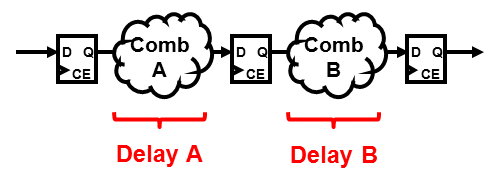

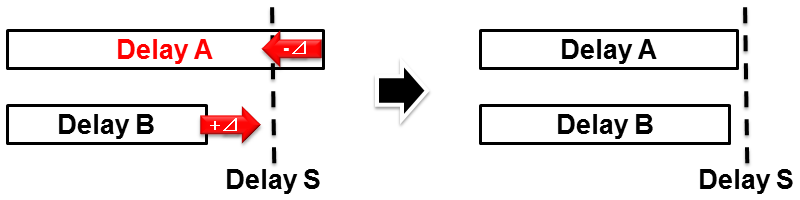

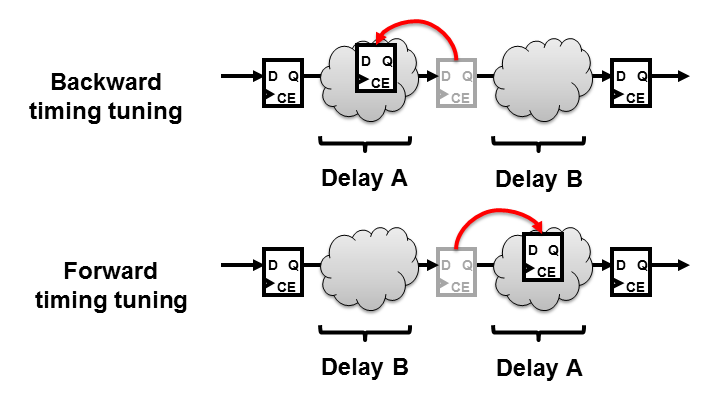

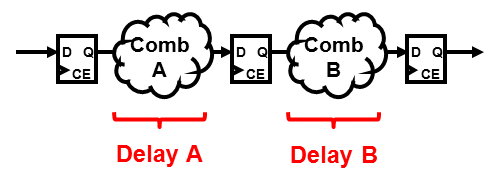

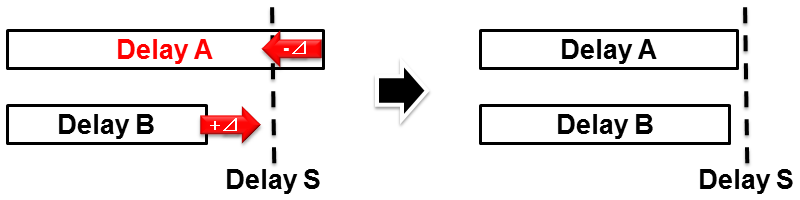

- 壓恾偺慻傒崌傢偣夞楬A偲慻傒崌傢偣夞楬B傪廲懕偝偣偨僷僀僾儔僀儞傪偛棗偔偩偝偄丅僔僗僥儉偺僞乕僎僢僩傪抶墑S偲偟丄抶墑A亜抶墑S亜抶墑B偲偟傑偡丅

- 婎杮揑側峫偊曽偼丄抶墑B偺梋桾暘偵廂傑傞傛偆抶墑A偺挻夁暘?傪堏摦偝偣傞偙偲偱偡丅旕忢偵扨弮偱娙扨側偙偲偱偡偑丄偙傟傪榑棟愝寁偱偳偆偡傞偐偲尵偆偙偲偑億僀儞僩偵側傝傑偡丅

婰弎曄峏偱偺懳墳1

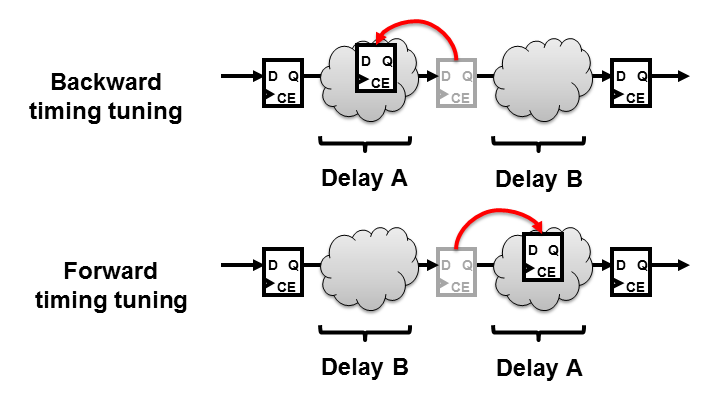

- 僞僀儈儞僌傪暘抐偡傞FF傪堏摦偝偣傞偙偲偵側傝傑偡偑丄偦傟偼慻傒崌傢偣夞楬偺拞偵擖傝崬傫偱偺懳墳傪堄枴偟傑偡丅挻夁抶墑A偲梋桾抶墑B偑偁傞偲偟偰丄挻夁抶墑A傪帩偮夞楬偑婰弎曄峏偺懳徾偵側傝傑偡丅

- 椺偊偽丄16價僢僩偳偆偟偺妡偗嶼傪儔僢僠偡傞僷僀僾儔僀儞僗僥乕僕偑抶墑挻夁偲壖掕偟傑偡丅怣崋a,b偼慜抜僗僥乕僕偺FF弌椡丄怣崋c偼屻抜僗僥乕僕偺慻傒崌傢偣夞楬擖椡偱偡丅

always @(posedge clk)

c[31:0] <= #1 a[15:0] * b[15:0];

- 埲壓偼16價僢僩偳偆偟偺妡偗嶼偼廳偄偺偱丄2偮偺妡偗嶼偵暘夝偟偰屻偱寢壥傪懌偟偙傓傕偺偱偡乮怣崋掕媊傪徣偄偰偄傞偨傔丄忕挿偱偡偑價僢僩儗儞僕傪婰嵹偟偰偄傑偡乯丅偙偺応崌偼丄忋恾偺屻曽抶墑挷惍偵側傝傑偡丅

always @(posedge clk) begin

c_h[31:8] <= #1 a[15:0] * b[15:8];

c_l[23:0] <= #1 a[15:0] * b[7:0];

end

assign c[31:0] = {c_h[31:8], 8'd0} + {8'd0, c_l[23:0]};

- 偝偰丄慜曽抶墑挷惍偼慜抜僗僥乕僕偺弌椡FF偵偼嵶岺偑昁梫偱偡丅幚嵺偵偼慜抜僗僥乕僕偺FF擖椡傪怣崋aD, bD乮D偼FF偺D抂巕擖椡偺堄枴乯偲偟丄偦偺怣崋偩偗傪巆偟偰FF帺懱偼嶍彍偟傑偡丅偙偺弨旛偺寢壥丄怣崋a, b仺怣崋aD, bD偵偡傞偩偗偱埲壓偺傛偆偵側傝傑偡丅

always @(posedge clk)

c_h[31:8] <= #1 aD[15:0] * bD[15:8];

c_l[23:0] <= #1 aD[15:0] * bD[7:0];

end

assign c[31:0] = {c_h[31:8], 8'd0} + {8'd0, c_l[23:0]};

- 忋婰偼堄恾揑偵慻傒崌傢偣夞楬傪暘妱偟傑偟偨偑丄拞娫揑側怣崋偑尦乆懚嵼偡傞偙偲偑寢峔偁傝傑偡丅偙偺応崌偼偦偺傑傑棙梡偟傑偡丅

婰弎曄峏偱偺懳墳2

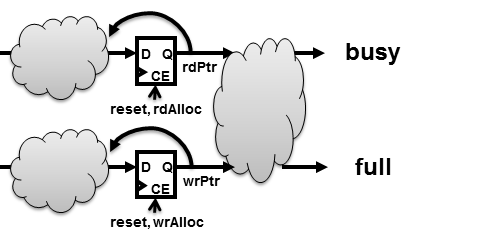

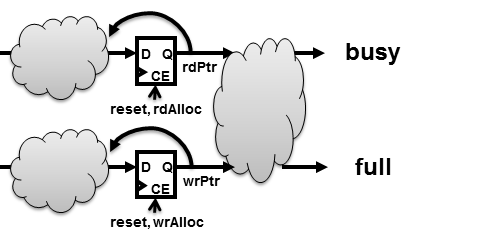

- 拞娫怣崋傪棙梡偡傞拲堄揰偼丄摨偠埵憡乮僗僥乕僕偺埵抲乯偺傕偺偩偗傪巊偆丄FF偺D抂巕偺怣崋偼CE抂巕偑側偄宍傪峫椂昁梫偑偁傝傑偡丅椺偊偽丄FIFO偺Busy, Full怣崋偑師偺傛偆偵掕媊偝傟偰偄傞偲偟傑偡丅徻偟偔偼愝寁椺FIFO傪嶲徠偟偰偔偩偝偄乮偨偩偟丄怣崋柤偺rd偲wr偼i偲o偵曄傢傝傑偡乯丅

always @(posedge clk)

if (reset)

rdPtr[3:0] <= #1 4'd0;

else if (rdAlloc)

rdPtr[3:0] <= #1 rdPtr[3:0] + 4'd1;

always @(posedge clk)

if (reset)

wrPtr[3:0] <= #1 4'd0;

else if (wrAlloc)

wrPtr[3:0] <= #1 wrPtr[3:0] + 4'd1;

assign busy = (rdPtr[3:0] != wrPtr[3:0]);

assign full = (rdPtr[3] != wrPtr[3]) & (rdPtr[2:0] == wrPtr[2:0]);

- Busy偲Full偼慻傒崌傢偣夞楬側偺偱丄屻乆偺偙偲傪峫偊抶墑0偮傑傝FF弌椡偟偨偔側傝傑偡丅偙偺応崌丄慜曽抶墑挷惍傪棙梡偟傑偡丅

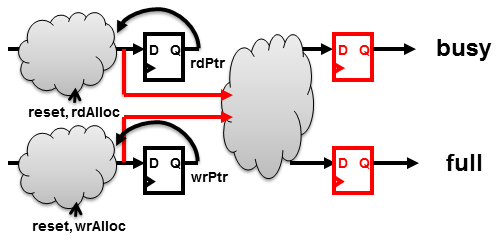

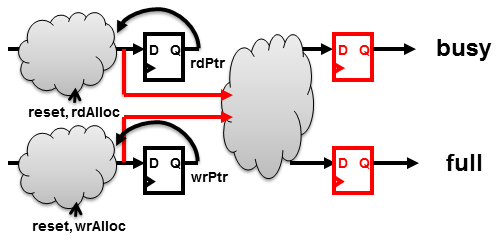

// CE抂巕偑側偄FF婰弎

always @(posedge clk) begin

rdPtr[3:0] <= #1 rdPtrD[3:0];

wrPtr[3:0] <= #1 wrPtrD[3:0];

busy <= #1 busyD;

full <= #1 fullD;

end

// D宆FF傊偺曄姺丄僔僗僥儉嫟捠偺儕僙僢僩偱偁傟偽reset怣崋偼昁偢偟傕擖傟傞昁梫偼側偄

// 乮曋棙偵巊偆D抂巕偲偟偰偼晄昁梫偩偑丄忋婰偺FF戙擖偺偲偙傠偱reset偼昁偢昁梫乯

assign rdPtrD[3:0] = reset ? 4'd0 : rdPtr[3:0] + rdAlloc;

assign wrPtrD[3:0] = reset ? 4'd0 : wrPtr[3:0] + wrAlloc;

// 忋婰D抂巕偲摨埵憡偺Busy, Full怣崋傪惗惉

assign busyD = (rdPtrD[3:0] != wrPtrD[3:0]);

assign fullD = (rdPtrD[3] != wrPtrD[3]) & (rdPtrD[2:0] == wrPtrD[2:0]);

- 埲忋偺傛偆偵丄Busy, Full怣崋傪惗惉偟偰偄偨assign暥偺巊梡偡傞怣崋傪慡偰慜偺僗僥乕僕偺FF偺D抂巕擖椡偵抲偒姺偊傞偙偲偵傛偭偰丄Busy, Full怣崋傪FF壔偡傞慜偺D抂巕怣崋偑惗惉偱偒傑偡乮FF偺堏摦偱偼側偔惗惉乯丅摦嶌丒寢壥偲傕椉幰偲傕慡偔摍壙偱偡丅

- 偙偙偱丄D抂巕埲奜偺怣崋傪巊偆偲埵憡偑偍偐偟偔側傝岆嶌摦偟偰偟傑偆偺偱拲堄偑昁梫偱偡丅傑偨丄FIFO偺億僀儞僞乕rdPtrD偲wrPtrD偼丄偦傟偧傟傪reset偲rdAlloc, wrAlloc娷傫偩弮悎側FF偺D抂巕怣崋偵偟側偗傟偽偄偗傑偣傫丅傛偔朰傟傞偺偑丄FF偺CE抂巕傪峫椂偟側偄偙偲偱偡乮CE抂巕偑側偄婰弎偵偡傞乯丅

夞楬僨僓僀儞 > 僥僋僯僢僋 > 抶墑偺堏摦 師偺儁乕僕乮僗僥乕僩儅僔儞乯 偙偺儁乕僕偺TOP 仯